Net-FPGA is a widely used FPGA-based platform for network experimentation, teaching and research. It integrates a low-cost FPGA-based networking board, which contains four 1 Gbps Ethernet interfaces with free open source software and gate ware. It enables researchers to explore new networking approaches with low startup investment.

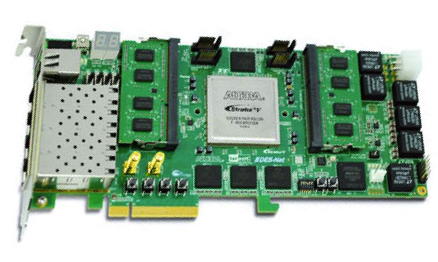

Today let us know about Terasic DE5-Net Stratix V GX FPGA Development Kit which provides the ideal hardware solution for designs that demand high capacity and bandwidth memory interfacing, ultra-low latency communication, and power efficiency. DE5 Net FPGA is an open source port of the Net FPGA platform on Altera DE5 board. DE5 Net FPGA provides network researchers with a powerful open platform to build complex network applications.

The Stratix® V GX FPGA features integrated transceivers that transfer at a maximum of 12.5 Gbps, allowing the DE5-Net to be fully compliant with version 3.0 of the PCI Express standard, as well as allowing an ultra low-latency, straight connections to four external 10G SFP+ modules. With a full-height, 3/4-length form-factor package, the DE5-Net is designed for the most demanding high-end applications, empowered with the top-of-the-line Altera Stratix V GX, delivering the best system-level integration and flexibility in the industry.

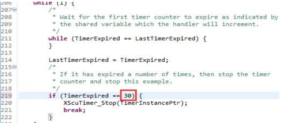

It depicts the layout of the board and indicates the location of the connectors and key components. Users can refer to this figure for relative location of the connectors and key components.

The DE5 board integrates the state-of-the art Stratix V GX FPGA 5SGXEA7N2F45C2. The key features of DE5 include:

Stratix V GX FPGA

- 5SGXEA7N2F45C2

- 622,000 logic elements (LEs)

- 50-Mbits embedded memory

- 48 transceivers (12.5Gbps)

- 512 18-bit x 18-bit multipliers

- 256 27-bit x 27-bit DSP blocks

- 2 PCI Express hard IP blocks 840 user I/Os

- 210 full-duplex LVDS channels

- 28 phase locked loops (PLLs)

JTAG Header and FPGA Configuration

- On-board USB Blaster II or JTAG header for use with the Quartus Prime Programmer

- MAXII CPLD EPM2210 System Controller and Fast Passive Parallel (FPP) configuration

Memory devices

- 32MB QDRII+ SRAM

- Up to 8GB DDR3 SO-DIMM SDRAM

- 256MB FLASH

General user I/O

- 10 user controllable LEDs

- 4 user push buttons

- 4 user slide switches

- 2 seven-segment displays

On-Board Clock

- 50MHz oscillator

- Programming PLL providing clock for 10G SFP+ transceiver

- Programming PLL providing clock for SATA or 1G SFP+ transceiver

Four Serial ATA ports

- SATA 3.0 standard at 6Gbps signaling rate

Four SFP+ ports

- Four SFP+ connector (10 Gbps+)

PCI Express x8 edge connector

- Support for PCIe Gen1/2/3

- Edge connector for PC motherboard with x8 or x16 PCI Express slot

Power Source

- PCI Express 6-pin DC 12V power

- PCI Express edge connector power

For designs that demand high capacity and high speed for memory and storage, the DE5-Net delivers with two independent banks of DDR3 SO-DIMM RAM, four independent banks of QDRII+ SRAM, high-speed parallel flash memory, and four SATA ports.

At last we can conclude saying that DE5-Net fully supports all high-intensity applications such as low-latency trading, cloud computing, high-performance computing, data acquisition, network processing, and signal processing.

Continued with this, there are a lot of activities (Workshops/Videos/Application notes) please stay tuned with our YouTube channel as well as blogs to learn more. (Website: https://www.tenettech.com/browse/fpga-6)

For any further assistance, please feel free to contact us at info@tenettech.com and we would be more than happy to help.